[24-OCT-24] The Telemetry Control Box (TCB) is a telemetry receiver for devices such as our Subcutaneous Transmitters (SCT), Implantable Inertial Sensors (IIS), or Implantable Stimulator-Transponders (IST). The TCB-A16 provides sixteen antenna inputs, to which we can connect up to sixteen coaxial antennas, such as the Loop Antenna (A3015C). Each antenna input is equipped with its own dedicated receiver and power meter. The telemetry messages we record with a TCB contain not only the telemetry channel number and sample value, but also the identity of the top antenna, which is the antenna at which the message presented the greatest microwave power, and the top power, which is a logarithmic measure of the microwave power at the top antenna. The top antenna is almost always the antenna closest to the animal, so the to TCB's top antenna measurement allows us to monitor the location of animals in mazes and other complex environments. The TCB-B16 provides all the functionality of the TCB-A16, but in addition allows us to use the sixteen antennas as command transmitters, and provides four programmable, high-speed, digital input-output signals. Command transmission allows us to control devices such as Implantable Stimulator-Transponders (ISTs). The digital communication lines allow the TCB-B16 to receive timing signals and transmit telemetry information to external devices.

The TCB requires only one network cable for communication and power, an industry-standard Power over Ethernet (PoE) connection. We supply the TCB with an Ethernet jumper cable so we can connect it to a PoE switch, and we sell high-reliability, fanless, PoE switches of various sizes for use with the TCB and our other PoE devices. When you order a TCB-A16, you can order up to sixteen Loop Antennas (A3015C) to go with it, depending upon how many you need to deploy in your telemetry system.

The TCB-A16 replaces our long-running Octal Data Receiver (A3027E, ODR) and LWDAQ Driver (A2071E) telemetry system. The TCB-A16 provides sixteen antenna inputs, the ODR provided eight. The TCB-A16 provides a top antenna measurment, the ODR does not. The TCB-A16 requires a PoE connection, the LWDAQ Driver required a 100-Base-T connection and a separate 24-V power adaptor. The TCB-B16 replaces the Command Transmitter (A3029C) and LWDAQ Driver (A2071E). The TCB-B16 provides sixteen independent, non-interfering command transmitters, the A3029C provided only one. The TCB-B16 requires no additional power supply for command transmission, the A3029C required its own 24-V power adaptor.

[01-OCT-24] The following versions of the Telemetry Control Box (A3042, TCB) are defined.

| Version | Dimensions | Comment |

|---|---|---|

| TCB-A16 | 55 cm × 35 cm × 12 cm | 16-way receiver, location monitor. |

| TCB-B16 | 55 cm × 35 cm × 12 cm | 16-way receiver, location monitor, command transmitter, digital I/O. |

The TCB-A16 went into production in January 2023. The TCB-B16 went into production in August 2024. The TCB-B16 provides command transmission through all sixteen antennas for controlling Implantable Stimulator-Transponders (ISTs). The TCB-B16 popluates the four holes X1-X4 on the back wall with four more BNC sockets. These will provide programmable, high-speed, digital input-output for experiments in which external stimuli need to be controlled in a manner synchronous with the telemetry signals, and in which synchronizing signals need to be embedded in the telemetry recording.

[01-MAY-25] The TCB obtains all its power and communication through a single Power-over-Ethernet (PoE) socket. The TCB system consists of the TCB, a PoE switch, coaxial cables, feedthroughs, and Faraday enclosures. In the paragraphs below, we provide detailed instruction on setting up the TCB for communication with your computer, but ultimately refer you to the SCT setup instructions once that communication is established.

Power Up PoE Switch: Connect power to your PoE switch. If you are not in the United States, you will need a computer power cable to connect to your local type of wall power socket, but you can be assured that the power adaptor will operate with any AC voltage 100-250 V, 50-60 Hz. Lights should illuminate on the PoE switch.

Connect TCB to PoE: Use a network cable to connect the TCB to the PoE switch. This cable can shielded or unshielded, and it can be up to ten meters long. Lights should illuminate on the TCB.

Install Software: Download and install the latest version of the LWDAQ software from here, following these installation instructions.

Connect Computer to PoE: Connect your data acquisition computer to the switch. Configure your computer to use its wired Ethernet interface with subnet 10.0.0.0 and IP address 10.0.0.20. The TCB ships with an IP address 10.0.0.x, where x is given by the last two or three digits of the serial number on the back of the TCB enclosure. The table below gives examples of serial numbers and their addresses.

| Serial Number | Address |

|---|---|

| Y61061 | 10.0.0.61 |

| Y61163 | 10.0.0.163 |

| P0148 | 10.0.0.148 |

| C0089 | 10.0.0.89 |

| Y70105 | 10.0.0.105 |

You should see a link light beside the sockets you have used on the PoE switch for your computer and your TCB. Launch the LWDAQ software and try to contact the TCB using the Configurator Tool, as described here. Don't proceed until you can contact the TCB and read its EEPROM.

Continue with Telemetry Setup: Connect antennas, set up software, and test out sample transmitters with the help of our Subcutaneous Transmitter (SCT) setup instructions, which you will find here.

Use the Neurorecorder to record telemetry data from the TCB. Use the Receiver Instrument, available with a button in the Neurorecorder, to view live data before it is written to disk. Use the Neuroplayer to view, analyze, and export the data during or after recording. In the Neuroplayer, use the Neurotracker to see which antenna is receiving the most power from each of your transmitters. Use the Stimulator Tool to send commands to your Implantable Stimulator-Transponders (ISTs).

[01-MAY-25] The TCB is a LWDAQ system of Form C, as described in the LWDAQ Specification. It consists of a relay, a controller, and a device with three elements. Device element one is the telemetry receiver, which consists of detector modules and the logic that reads them out and stores their messages in a buffer. Device element two is the telemetry transmitter, which consists of transmitter modules and the logic that organises them. Device element three is the digital interface, which consists of four digital input-output (DIO) signals. These signals appear on four BNC connectors X1-X4 on the back wall of the TCB. The TCB-A16 provides only element one. The TCB-B16 provides all three elements. The TCB implements the LWDAQ command job. We use command jobs to reset the telemetry receiver, transmit telemetry commands, and configure the digital interface. Because the TCB does not implement driver sockets or multiplexer sockets, we do not need to write to a device address register to select which socket for the command job. But we must write to the device element register to tell the controller if the command is destined for the telemetry receiver (1), telemetry transmitter (2), or digital interface (3).

To communicate with the TCB, our data acquisition software composes messages in the LWDAQ-TCPIP message format that read to and write from its controller address space. This space is defined in the file Main.vhd of the P3042BB firmware.

-- Relay Interface Memory Map Constants with Read and Write as seen by the -- LWDAQ Relay that is master of the interface. We respect the existing -- allocation of controller addresses given in the A2071 manual. constant cont_id_addr : integer := 0; -- Hardware Identifier (Read) constant cont_sr_addr : integer := 1; -- Status Register (Read) constant cont_djr_addr : integer := 3; -- Device Job Register (Read/Write) constant cont_der_addr : integer := 15; -- Device Element Register (Write) constant cont_hv_addr : integer := 18; -- Hardware Version (Read) constant cont_fv_addr : integer := 19; -- Firmware Version (Read) constant cont_crhi_addr : integer := 32; -- Command Register HI (Write) constant cont_crlo_addr : integer := 33; -- Command Register LO (Write) constant cont_di_lo : integer := 38; -- Digital Inputs LO (Read) constant cont_cfsw_addr : integer := 40; -- Configuration Switch (Read) constant cont_srst_addr : integer := 41; -- Software Reset of Controller (Write) constant cont_fifo_av_addr : integer := 61; -- Fifo Blocks Available (Read) constant cont_fifo_ds_addr : integer := 62; -- Fifo Data Strobe (Read/Write) constant cont_fifo_rd_addr : integer := 63; -- Fifo Read Portal (Read)

The hardware identifier, hardware version, and firmware version number registers provide values that allow us to determine which type of receiver we are trying to read out and control. These are values made available by all LWDAQ systems. The LWDAQ Configurator Tool reads these values and presents them to us when we contact a LWDAQ Relay, such as the relay provided by the TCB. We read them out with our LWDAQ_byte_read routine, which in turn uses the LWDAQ byte read instruction to access the byte.

[01-MAY-25] The TCB detector modules are read out along a daisy-chain bus. Each detector module has both upstream and downstream data buses and upstream and downstream data strobes. The modules share eight common lines in the detector control bus. Each detector module can assert Message Ready (MRDY), after which the base board telemetry receiver logic will use Detector Module Read Control (DMRC) and its upstream data strobe to read the message from the closest module in the chain. After that, it will read the same or a different message from a farther module in the chain. If it reads the same message, but with a greater power, it discards the previous message. The message that is stored in the telemetry receiver's data buffer

The telemetry data is stored in a first-in, first-out (FIFO) buffer that we access through the Fifo Read Portal (63). To begin recording telemetry data from a TCB, we must first reset the telemetry receiver, which we do with the help of byte write instructions. See Receiver.tcl for a complete presentation of the management of TCB readout. We use LWDAQ_set_device_element to set the Device Element Register to one (1). We use LWDAQ_transmit_commant_hex to transmit 0x0081 to the telemetry receiver, and this command causes the reset. Now we read Fifo Blocks Available with LWDAQ_byte_read and multiply by 512 to get the number of bytes available. The maximum value of this counter is 255, so if there are more than 130 kBytes of data available, you will not know it, even though the FIFO is 2 MBytes long. We then use LWDAQ_ram_read to fetch the available data. This routine uses the LWDAQ stream read instruction to read data out of the buffer portal. The LWDAQ Relay, which provides the TCPIP interface, uses Fifo Data Strobe (62) is used to punctuate its communication with the LWDAQ Controller, which provides the FIFO. See C3038A01.c for the code that runs on the RCM6700 that provides the LWDAQ Relay function. For details of the LWDAQ Controller, see the comments in Main.vhd and CPU_ROM.asm.

The TCB telemetry data consists of six-byte message. Each message begins with a four-byte telemetry message record, which we describe in the Telemetry User Manual. After that comes the top power and the top antenna, each one byte. When we download from the TCB, we must download a whole number of messages, so the number of bytes we download should be divisible by six. If the bytes available is 255 × 512 Bytes, we can download 21760 Bytes, and then read the bytes available a second time. Eventually, we will get all the available data.

[01-MAY-25] The TCB-B implements a multi-channel command transmitter for radio-controlled implants by commandeering the reception antennas for command transmission. We present the command transmission protocol in detail in the Implantable Stimulator-Transponder (A3041) manual. We reproduce below the timing diagram from the protocol.

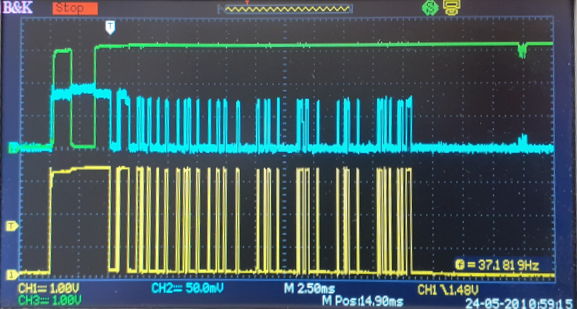

A typical command transmission lasts 10-40 ms. During this time, all TCB-B antennas are connected to their own dedicated radio-frequency power source whenever the command transmission requires that a HI be transmitted. The power sources turn on and off so quickly that we can disconnect them and turn them off during each LO level. During these LO periods, the TCB can receive telemetry signals. Reception will drop to around 50% during command transmission, and recover immediately afterwards. The traces below show an IST responding to a command transmitted by a single TCB-B16 antenna. Command reception is >90% for ranges ≤30 cm.

The transmitting feedthrough provides one transmitter module and one radio-frequency switch for each of its antenna connections. These antenna connections are no longer strictly "inputs" because they will occasionally act as outputs. Electrical power for the transmitter modules on the TCB-B16 is provided by a lithium-ion battery. Each transmitter module takes as input an !ON signal. When the transmitting feedthrough asserts ON, the radio-frequency switch connects the antenna to the transmitter module and the transmitter module itself turns on its radio-frequency oscillator. Roughly 21 dBm of 917-MHz radio-frequency power will appear on the antenna connector. When ON is not asserted, the antenna is connected through the transmitting feedthrough to a detector module on the TCB base board and the transmitter module's oscillator is deprived of electrical power. No oscillation and no radio-frequency power produced. Each transmitter module mounts on a 5 × 2 socket header at one end and is held at the other end by a standoff and screw. The electrical power and control enter through the header. The radio frequency power exits through a UMCC connector that we connect with a 50-mm cable to another UMCC jack next to the antenna switch.

On the TCB-B16, the transmitting feedthrough logic is provided by an LCMXO2-4000ZE field-programmable gate array. Connection to the base board is via four flying wires terminated in a MOLEX-4 socket. These four wires carry +5V, 0V, TX, and RX. The logic chip receives instructions from the base board via TX and sends notifications back to the base board via RX. Instructions enable antennas, transmit telemetry command bytes, and configure the four digital input-outputs.

The transmitting feedthrough logic chip runs off 1.2 V and 3.0 V, both of which we regulate down from +5V. Power for the transmitter modules, however, is provided by a 380 mAhr high-current, lithium-polymer battery. Rated for 25C discharge, this battery can deliver 9.5 A for one or two seconds. The battery includes its own overvoltage, undervoltage, overcurrent, and short circuit protection. It mounts on the wall of the TCB enclosure and connects with a short cable and two-way socket. The battery charger is a 70-mA current source with 4.1-V voltage limit. Because the transmitter modules are active for less than 1% of the time, the 70-mA charger is sufficient to restore the battery after bursts of 16 × 0.3 = 4.8 A. When on the shelf without power, the battery is disconnected from the circuit by a mosfet switch. Lithium-polymer batteries discharge at approximately 5% per month. The battery could drain to 15% capacity in three years without power. After that, the 70-mA current source will restore the battery to 25% capacity in half an hour.

On each transmitter module, we have a TLV61048 boost regulator producing +5.0 V from VBAT = 3.7 V with 90% effiency. These run all the time, consuming roughly 100 μA with no load. We have a mosfet switch to connect power to our RF oscillator and amplifier. There are two stages of RF amplification, both use SOT-89 packages. The oscillator can use the GALI-3+ . With feedback through a 50-mm delay line and a 915-MHz SAW filter, we get our oscillation with +10 dBm output after stabilizing attenuator. The next stage can be GVA-92+ providing 25 dBm when saturated. The GVA-92+ requires no output matching network at 900 MHz. The recommended input matching network of 18 nH parallel followed by 5.6 pF series is designed to match a 50-Ω source to a load of 40 + 10j Ω. We omit this network with no loss of performance. We add a 2-dB attenuator and a 1-GHz low-pass filter to the output to produce 23 dBm with minimal harmonics. We launch this power off the board with a UMCC jack. Total current consumption from +5V is 200 mA, or 300 mA from VBAT. By the time the signal gets through the radio frequency switch and the BNC connector on the back wall of the TCB enclosure, we have 21 dBm.

The Stimulator Tool manages transmission of commands to ISTs as well as decoding their acknowledgements and metadata messages. The Stimulator.tcl source code shows how we manage command transmission. The Stimulator_transmit routine is the one that connects to the TCB and sends the LWDAQ commands that cause the transmitter modules to generate the telemetry command. After selecting device element two (2), we use command jobs to transmit a series of sixteen-bit commands through the base board logic to the transmitting feedthrough logic. The bottom seven bits (DC1-DC7) of these commands specify an operation. The eighth bit (DC8) is always one. The top eight bits (DC9-DC16) provide an operand for the operation. Here are the transmitting feedthrough operations.

-- Instruction Op-Codes constant rf_off_op : integer := 0; -- Turn off the RF transmitter. constant rf_on_op : integer := 1; -- Turn on the RF transmitter. constant rf_xmit_op : integer := 2; -- Transmit a command byte. constant tm_test_op : integer := 3; -- Transmitter Module test.

The rf_on operation ignores the operand and turns on all the transmitters for 5.00 ms. On a TCB-B16, full power will be drawn for these 5 ms, then all the transmitters turn off and the job is done. The rf_off operation makes sure all the transmitters are off. The rf_xmit operation takes the top eight bits and transmits them through all transmit modules at the same time, using the protocol pictured above. The tm_test operation is for calibration and testing: it turns on one and only one transmit module continuously. The operand gives the number of the antenna socket that will be producing power.

The LWDAQ software's Diagnostic Instrument provides a means to control the transmit modules. In the Diagnostic Instruments info panel, set daq_device_element to 2. Enter your TCB's IP address in daq_ip_addr. Enter "0183" in the command box and press "Transmit". Transmit module number one, which is connected to antenna number one, will turn on and stay on. Enter "0080" in the command box and press "Transmit" to turn it off.

[01-MAY-25] The digital input-output (DIO) signals provided by the digital interface in the TCB-B devices appear as X1-X4 on the back wall of the enclosure, where they are presented by four BNC sockets. Each of these DIO signals is controlled by three connections to the transmitting feedthrough logic. These are Output Enable (XEN1-XEN4), Output Data (XD1-XC4), and Clamped Input (XC1-XC4). When XEN1 is asserted, an SN74LVC1G126 drives X1 with XD1 through 50 Ω. We power the 1G126 with 5 V so that it can provide 2.5-V down a 50-Ω coaxial cable. By enabling the SN74LVC1G126 and setting XD low, we provide 50-Ω termination for the X1 input. The value XC1 is a clamped version of X1 for input. On the transmitting feedthrough, the logic chip is far from the X1-X4 sockets. We connect each of X1-X4 to the transmitting feedthrough with a 150-mm BNC to UMCC cable, but we still have 400 mm from the end of the coaxial cable to the logic chip. We run the logic signal down a 50-Ω microstrip transmission line to the terminating 50-Ω resistor next to the logic chip.

To configure the digital interface, we select device element three (3) and use the command job to transmit an operation code and operand. We list the operations below. As with the commands we send to the telemetry transmitter on the transmitting feedthrough, these op-codes make up the bottom seven bits of the command (DC1-DC7), while the eighth bit (DC8) is always one, and the top eight bits (DC9-DC16) contain an operand.

-- Instruction Op-Codes constant dio_en_op : integer := 8; -- Enable or disable digital outputs. constant dio_set_op : integer := 9; -- Set or clear digital outputs.

The dio_en operation uses the operand to enable the four digital outputs. Bits 0-3 (DC9-DCof the operand enable digital output X1-4 respectively. Now the digital input-output becomes an output. The dio_set operation sets the value of the digital outputs. Bits 0-3 set the value of outputs X1-4. When we disable an output, its output value is not driven onto the digital input-ouput signal. But as soon as we enable the output, this same value will be driven onto the signal once again.

The digital state of X1-X4, as well as whether or not each of the outputs is enabled, will be reported by the transmitting feedthrough to the base board logic once every 256 μs. We read the four signal values and the four enable values from the Digital Inputs location (38) in the control address space. To read the byte we use LWDAQ_byte_read, which in turn uses the LWDAQ byte read instruction. The LWDAQ software's Diagnostic Instrument provides immediate access to the TCB digital inputs and outputs for diagnostic purposes. In the Info Panel, set daq_device_element to 3. Enter your TCB's IP address in daq_ip_addr. Enter "0F88" in the command box and press "Transmit". The digital outputs are now enabled. Enter "0F89" and press "Transmit" to set them all HI. The HI voltage will be +5 V when open-circuit and +2.5 V when terminated with 50 Ω. Enter "0089" to set them all LO again, and they will all be 0 V. Now enter "0F89 0089" in the command box, "1000000" in the Repeat box and press "Transmit". You will see the outputs toggling.

[30-MAY-24] The TCB-A16 consumes a maximum of 8 W. The TCB-B16 peak power consumption during command transmission is 22 W. The extra 14 W is consumed by its sixteen quarter-watt radio-frequency power sources. This additional 14 W is drawn from the TCB-B16's on-board LiPo battery, which supplies 4.0 A during power transmission. This 14 W remains internal to the TCB-B16 because it must be drawn from the battery. The only power the battery draws from the TCB main power supplies is its re-charge current, which is at most 100 mA from 5 V, or 0.5 W. The logic and lamps on the TCB-B16's transmitting feedthrough consume no more than 0.5 W, so the average current consumption of the TCB-B16 cannot exceed 9 W. Command transmission is rare, so the TCB-B16's battery has plenty of time to recharge between transmissions.

[09-MAY-25] We make the TCB-A16 by taking an Animal Location Tracker (ALT) Base Board (A3038BB-D2), putting it in a box, populating it with ALT Detector Modules (A3038DM-B2), connecting the detector modules to a Sixteen-Way Straight Feedthrough (A3042SF-A) on the back wall of the box, connecting a Display Panel (A3042DP-A) to the base board, and fastening the display panel to the front of the box. We connect the ALT's RJ-45 socket to an RJ-45 feedthrough on the back wall of the box.

The TCB-B16 is identical to the TCB-A16 except its antenna connections pass through a Sixteen-Way Transmitting Feedthrough (A3042TF) equipped with sixteen Transmitter Modules (A3042TM). These additional circuits provide command transmission for Implantable Stimulator-Transponders (ISTs) as well as programmable, high-speed, digital input-output on the X1-X4 BNC sockets on the back wall.

| Version | Description | Comments |

|---|---|---|

| A3038BB-D2 | Base Board | An ALT base board, no detector coils, firmware P3042BB, active. |

| A3038DM-C2 | Detector Module | An ALT detector module, unshielded, firmware P3042DM, active. |

| A3038DM-D3 | Detector Module | An ALT detector module, shielded, firmware P3042DM, active. |

| A3042DP-A1 | Display Panel | Lamps and switches, firmware P3042DP, superceded. |

| A3042DP-A2 | Display Panel | Lamps and switches, firmware P3042DP, active. |

| A3042SF-A1 | Straight Feedthrough | Sixteen-way feedthrough, no filter, active. |

| A3042FF-A1 | Filtering Feedthrough | Sixteen-way feedthrough, with attenuators and filters, abandoned. |

| A3042TF-A1 | Transmitting Feedthrough | Sixteen-way transmitting feedthrough, active. |

| A3042TM-A1 | Transmitter Module | Prototype command transmitter, superceded. |

| A3042TM-A2 | Transmitter Module | Command transmitter, +21 dBm, 918±1 MHz, active. |

The P3042BB firmware is for the logic chip on the base board. This firmware is similar to the ALT Base Board firmware except for the addition of communication with the display board and transmitting feedthrough. We use C3038BB for the RCM6700 module, same code as for the ALT LWDAQ Relay. We use P3042DM on the detector modules. The detector modules themselves are the same A3038DM modules we use on the ALT, but they are re-configured for top antenna detection. We use P3042DP on the display panel, and P3042TF on the transmitting feedthrough.

S3042DP_1.gif: Schematic of A3042DP-A Display Panel.The table below gives the connection arrangement between the detector modules (DM) and the antenna inputs (AI) on the feedthrough. We make these connections with UMCC-terminated coaxial cables of various lengths. The number assigned to each detector module in the table is the number used in the name of the detector module on the circuit board silk screen. The module marked "DM4" is "Number Four". The number assigned to each antenna input is the number on the back face of the enclosure, and also on the feedthrough printed circuit board.

For details of the operation of telemetry reception by the A3042BB base board and A3042DM detector module, see the Animal Location Tracker (A3038) manual. The TCB uses the same base board and detector modules as the ALT, the only differences being in firmware and the fact that the TCB antennas are not loaded onto the base board. For a description of how we communicate with the TCB ove TCPIP, see the Operation: Communication section of this manual.

[24-DEC-22] The A304201A PCB for the display panel needs the following. Test points must be marked on back side of board. Need test points for detector control bus signals, marked on both sides. Two more mounting holes to stop the board from flexing.

[24-APR-24] In order to build the A3042TF-A1 using the A304202C printed circuit board, we perform the following modifications.

[14-AUG-24] Up until 24-APR-24 we apply the Detector Module Clock Modification, see A3038 Modifications, to the A3038BB-D2. We add C48 = 100 pF to the base of DMCK to reduce reflections off the end of the daisy chain. This modification is later superceded by the DMCK Termination Modification. In the DMCK Termination modification, we replace R41 with 47 Ω in series with 1.0 μF.

[15-NOV-24] For details of the development and production of the A3042 series circuits, see their Developement page.